据韩媒报道,苹果公司已决定在下一代M5芯片中放弃台积电的2nm工艺,转而沿用3nm工艺。

这一决策背后,主要是由于2nm工艺的高昂成本。

目前,台积电2nm工艺的单片硅晶圆报价高达3万美元,且良率仅为60%,这使得苹果不得不重新评估其芯片制造计划。

相反,3nm工艺在成本和成熟度上更具优势,能够更好地满足苹果当前的需求。

此外,苹果M5芯片还将采用台积电的SoIC封装技术,这是台积电最新的封装方案。

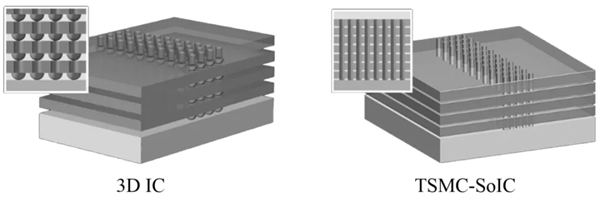

具体来说,SoIC的全称是System-on-Integrated-Chips,即集成片上系统。

这是一种创新的多芯片堆叠技术,通过将多个芯片垂直堆叠并集成在一起,形成一个三维的集成电路结构。

这种技术能够显著提升芯片的集成度,同时降低功耗并优化性能表现。

尽管M5芯片并未采用更先进的2nm工艺,但通过3nm工艺和SoIC封装技术的结合,苹果依然有望在性能和能效方面实现显著提升。

文章来源:快科技

据韩媒报道,苹果公司已决定在下一代M5芯片中放弃台积电的2nm工艺,转而沿用3nm工艺。

这一决策背后,主要是由于2nm工艺的高昂成本。

目前,台积电2nm工艺的单片硅晶圆报价高达3万美元,且良率仅为60%,这使得苹果不得不重新评估其芯片制造计划。

相反,3nm工艺在成本和成熟度上更具优势,能够更好地满足苹果当前的需求。

此外,苹果M5芯片还将采用台积电的SoIC封装技术,这是台积电最新的封装方案。

具体来说,SoIC的全称是System-on-Integrated-Chips,即集成片上系统。

这是一种创新的多芯片堆叠技术,通过将多个芯片垂直堆叠并集成在一起,形成一个三维的集成电路结构。

这种技术能够显著提升芯片的集成度,同时降低功耗并优化性能表现。

尽管M5芯片并未采用更先进的2nm工艺,但通过3nm工艺和SoIC封装技术的结合,苹果依然有望在性能和能效方面实现显著提升。

文章来源:快科技

Intel两年裁员多达2.3万人!全球员工仍然超过10万

4天前

不堪美国关税压力!华擎显卡等生产线搬出中国

4天前

全球人形机器人产业链百强发布:中国占据63%

4天前